컴퓨터는 어떻게 설계되어 있을까?

라는 질문에 대한 대답은 무궁무진하다.

컴퓨터를 이루는 부품은 파고들수록 다양하며 한 번에 나열하기 힘들 정도로 많다. 그러나 이러한 것들을 실질적으로 동작하게 만드는 내부 회로를 이해하면, 컴퓨터의 동작 과정과 설계 원리에 대해 한 걸음 더 가까워질 수 있다.

컴퓨터를 돌아가게 하는 것은 CPU이다. 그렇다면 CPU를 돌아가게 하는 것은? CPU는 어떻게 연산하는가?

이제부터 전자회로의 세계로 빠져들어, 컴퓨터를 보다 깊게 이해해 보자.

조합 논리회로

임의의 시점에서의 출력 값이 그 시점의 입력 값에 의해서만 결정되는 논리회로로, 기본적인 논리소자로 구성되어 있다. 즉 output을 오직 input만이 결정한다. 내부 기억능력 즉, 메모리를 갖지 않는다.

NOT, AND, OR, XOR, NOR, NAND, 반가산기, 전가산기, 디코더, 인코더, 멀티플렉서, 디멀티플렉서 등이 있다.

Adder(가산기)

덧셈을 수행하는 논리회로.

2개 이상의 input을 받아 output으로 합의 결과를 반환하며, 대부분 2진수의 합을 계산한다.

Half Adder(반가산기)

1비트씩을 사용하는 두 개의 입력과 두 개의 출력으로 합과 자리올림이 사용된다. 두 입력 변수에서 다음과 같은 연산이 가능하다.

진리표와 논리회로, 논리기호는 다음과 같다. sum은 A와 B의 XOR이고, carry는 A와 B의 AND임을 알 수 있다.

Full Adder(전가산기)

두 2진수 입력과 하위비트에서 발생한 자리 올림수를 포함하여 2진수 총 3개를 덧셈 연산한다.

진리표와 논리회로, 논리기호는 다음과 같으며, 두 개의 반가산기를 OR한 구조로 되어있다.

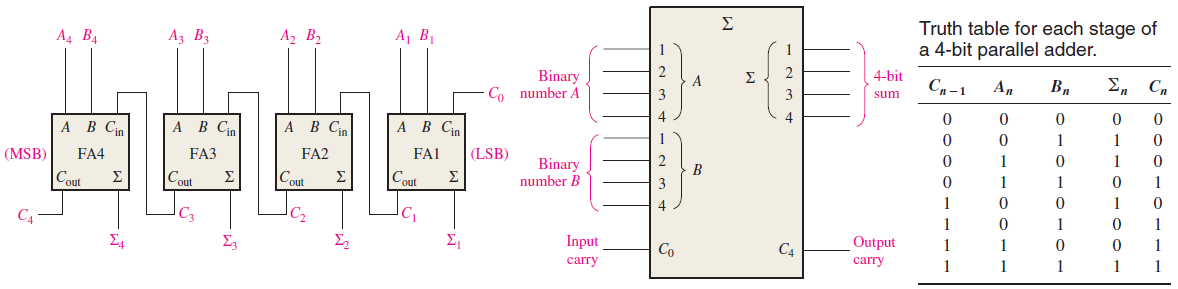

병렬 가산기

전가산기를 병렬로 연결하여 여러 비트로 구성된 2진수의 덧셈 연산을 수행한다. 직렬 가산과 달리 병렬로 가산할 경우 비트를 한꺼번에 계산하게 된다. 다음은 4개의 전가산기를 병렬로 연결한 병렬 가산기이다.

Subtractor(감산기)

두 개 이상의 입력에서 하나의 입력으로부터 나머지 입력들을 뺄셈해서 그 차를 출력하는 조합 논리회로.

가산기를 응용한 것이기 때문에 가산기의 sum(합)이 감산기에서는 difference(차)가 되고, 가산기의 carry(올림수)가 감산기에서는 borrow(빌림수)가 된다.

Half Subtractor(반감산기)

두 입력 간의 뺄셈으로 얻은 결과가 출력에서 차가 되고, 이 차가 음의 값을 갖는 경우 출력에서 빌림수과 활성화된다. 두 입력 변수에서 4가지 연산이 가능하다.

진리표, 회로도, 논리기호이다. D는 A와 B의 XOR, Br은 A의 NOT과 B의 OR이다.

Full Subtractor(전감산기)

반감산기가 단지 두 입력간의 차이를 구하는 논리회로였다면, 전감산기는 추가적으로 하위 비트에서 요구하는 빌림수에 의한 뺄셈까지도 수행한다.

가산기 때와 마찬가지로 반감산기 2개를 연결한 구조이다.

병렬 가감산기

디지털 장치에서는 별도로 감산기를 사용하지 않으며, 가산기에 게이트를 추가하여 부호 선택신호로 뺄셈 연산을 수행한다.

4비트 병렬 가감산기

입력 B에 XOR 게이트를 추가하여 부호를 선택할 수 있게 한다.

- XOR 입력(부호 선택 값이) 0 → 덧셈 연산 수행

- XOR 입력(부호 선택 값이) 1 → 뺄셈 연산 수행

![[논리회로] 조합 논리회로, 가산기와 감산기](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FyKADu%2FbtrFptV704v%2FAAAAAAAAAAAAAAAAAAAAAJiDnAAsmXI2od_V9E4d9GYC3vAX1i6k8OoPNUs3LFYR%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1761922799%26allow_ip%3D%26allow_referer%3D%26signature%3DGCVDP0ckr519kblXdFGPBoRo9nw%253D)